# Nanochannel fabrication and characterization using bond micromachining

Jeroen Haneveld

The research described in this thesis was carried out at the Transducers Science and Technology Group of the MESA<sup>+</sup> Research Institute at the University of Twente, Enschede, The Netherlands. The project was financially supported by the Dutch Technology Foundation (STW).

## Promotiecommissie:

Voorzitter

Prof. dr. ir. A.J. Mouthaan Universiteit Twente

Secretaris

Prof. dr. ir. A.J. Mouthaan Universiteit Twente

Promotor

Prof. dr. M.C. Elwenspoek Universiteit Twente

Assistent promotor

Dr. ir. H.V. Jansen Universiteit Twente

Leden

Prof. dr. ir. A. van den Berg Universiteit Twente

Prof. dr. ir. J.P. Brugger École Polytechnique Fédérale de Lausanne

Prof. P. Enoksson Chalmers University of Technology

Prof. dr. F.G. Mugele Universiteit Twente

Dr. J.G.E. Gardeniers Universiteit Twente

Referent

Dr. ir. N.R. Tas

Universiteit Twente

Haneveld, Jeroen

Nanochannel fabrication and characterization using bond micromachining

Ph.D. Thesis, University of Twente, Enschede, The Netherlands

ISBN: 90-365-2312-5

Copyright © 2006 by J. Haneveld, Lochem, The Netherlands

# NANOCHANNEL FABRICATION AND CHARACTERIZATION USING BOND MICROMACHINING

## **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof. dr. W.H.M. Zijm,

volgens het besluit van het College voor Promoties

in het openbaar te verdedigen op

vrijdag 20 januari 2006 om 16.45 uur

door

Jeroen Haneveld geboren op 28 augustus 1977 te Lochem Dit proefschrift is goedgekeurd door de promotor en de assistent promotor:

Prof. dr. M.C. Elwenspoek

Dr. ir. H.V. Jansen

# Index

| 1 | Introduction                                                             | 9  |

|---|--------------------------------------------------------------------------|----|

|   | 1.1 Nanochannels                                                         | 10 |

|   | 1.2 Micromachining technology as a tool for nanochannel fabrication      | 11 |

|   | 1.2.1 Bulk micromachining                                                | 12 |

|   | 1.2.2 Surface micromachining                                             | 15 |

|   | 1.2.3 Bond micromachining                                                | 15 |

|   | 1.3 Applications of nanochannels                                         | 16 |

|   | 1.4 Fabrication technologies for nanochannels                            | 17 |

|   | 1.5 Aim of this thesis                                                   | 19 |

|   | 1.6 Thesis outline                                                       | 20 |

|   | 1.7 References                                                           | 21 |

|   |                                                                          |    |

| 2 | Fabrication of 1D nanochannels                                           | 25 |

|   | 2.1 Wet anisotropic etching of <110> silicon for 1D fluidic nanochannels | 26 |

|   | 2.1.1 Etchant selection                                                  | 26 |

|   | 2.1.2 Mask material selection                                            | 28 |

|   | 2.1.3 Basic fabrication process                                          | 29 |

|   | 2.1.4 Etch rate calibration of silicon in OPD 4262 developer             | 30 |

|   | 2.1.5 Direct bonding of etched wafers to silicon and Borofloat glass     | 34 |

|   | 2.1.6 Channel fabrication and bonding results                            | 34 |

|   | 2.1.7 Conclusions                                                        | 37 |

|   | 2.2 Fabrication of nanochannels using a dry oxide spacer layer           | 38 |

|   | 2.2.1 Basic fabrication process                                          | 38 |

|   | 2.2.2 Dry oxidation of silicon                                           | 39 |

|   | 2.2.3 (B)HF etching of channels                                          | 45 |

|   | 2.2.4 BHF overetch determination                                         | 40 |

|   | 2.2.5 Bulk etching of silicon using 1% HF and BHF                        | 50 |

|   | 2.2.6 TEM measurements of the BHF overetch effect                        | 52 |

|   | 2.2.7 Direct bonding procedure to silicon and Borofloat glass            | 52 |

|   | 2.2.8 Channel fabrication and bonding results                            | 53 |

|   | 2.3 Conclusions                                                          | 55 |

|   | 2.4 References                                                           | 50 |

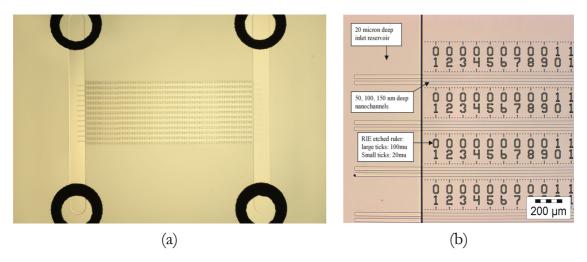

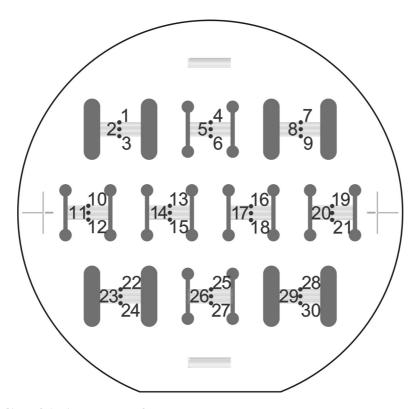

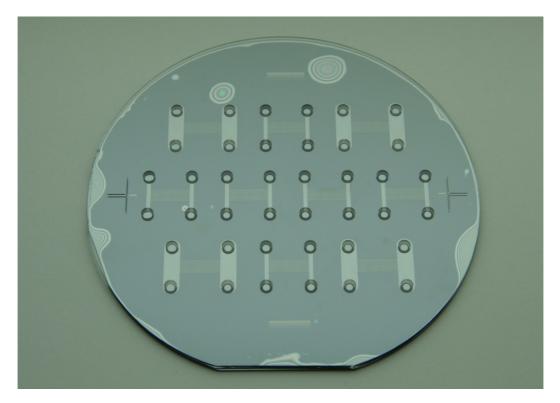

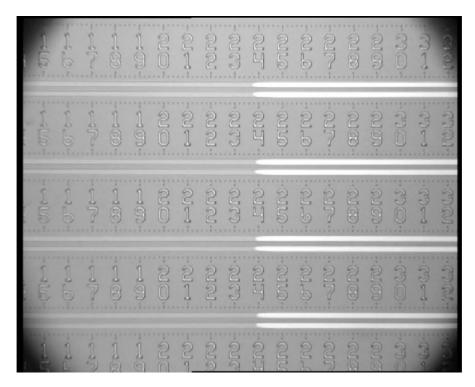

| 3 | Nanochannel chip fabrication                                                 | 59  |

|---|------------------------------------------------------------------------------|-----|

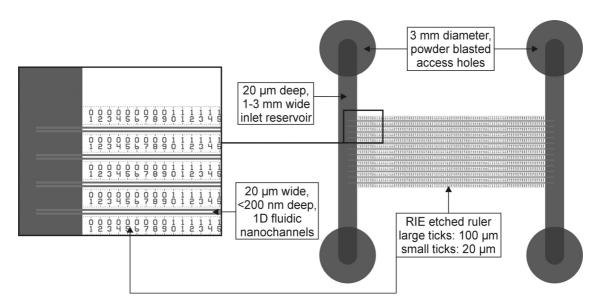

|   | 3.1 Chip design                                                              | 60  |

|   | 3.2 Fabrication of chips using wet anisotropic etching of <110> silicon      | 61  |

|   | 3.2.1 Fabrication procedure                                                  | 61  |

|   | 3.2.2 Fabrication results                                                    | 63  |

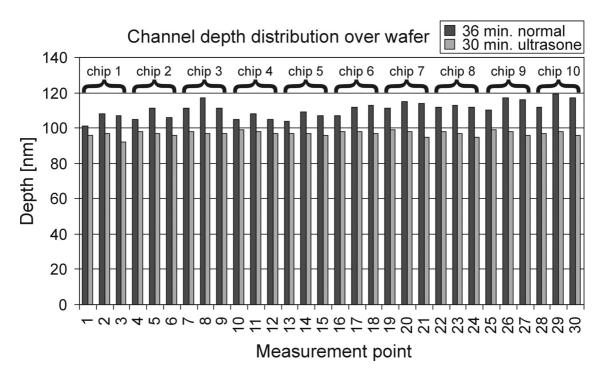

|   | 3.3 Fabrication of chips using a dry oxide spacer layer                      | 66  |

|   | 3.3.1 Fabrication procedure                                                  | 67  |

|   | 3.3.2 Fabrication results                                                    | 69  |

|   | 3.4 Conclusions                                                              | 74  |

|   | 3.5 References                                                               | 74  |

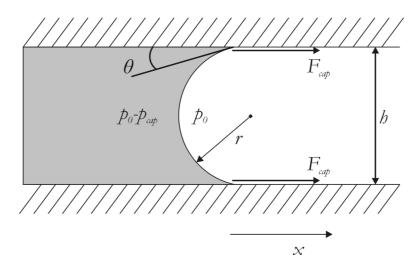

| 4 | Modeling and filling experiments                                             | 75  |

|   | 4.1 Introduction                                                             | 76  |

|   | 4.2 Capillary filling model                                                  | 76  |

|   | 4.3 Filling experiments using 150, 100 and 50 nm deep channels               | 79  |

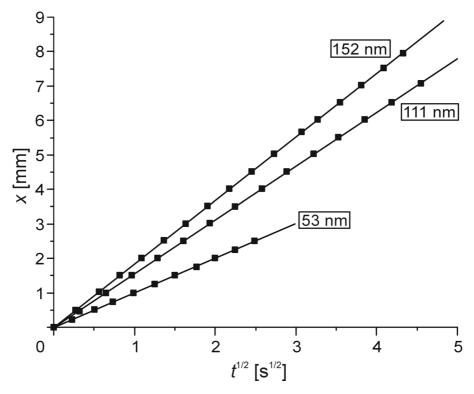

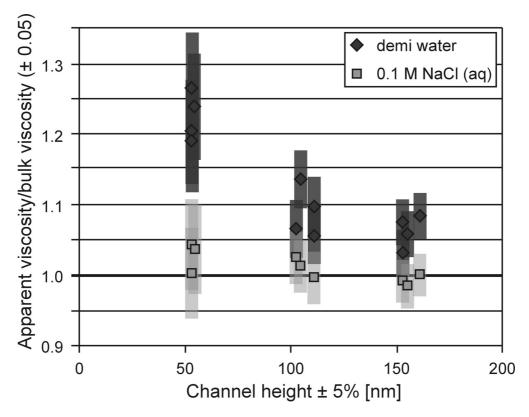

|   | 4.3.1 Experimental data                                                      | 79  |

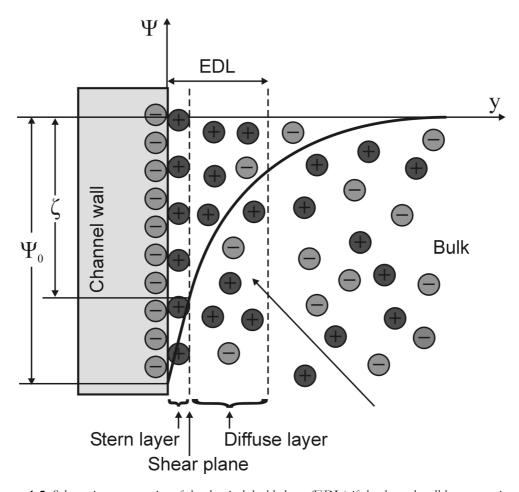

|   | 4.3.2 Electroviscous effects                                                 | 85  |

|   | 4.4 Filling experiments using 5, 11, 25 and 50 nm deep oxide spacer channels |     |

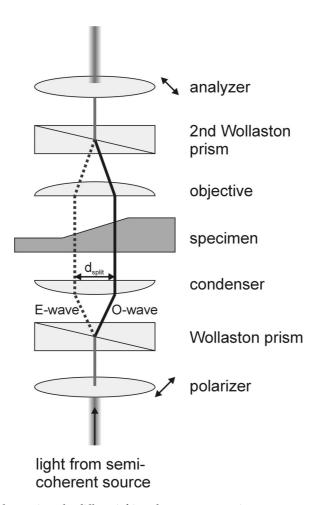

|   | 4.4.1 Introduction in DIC microscopy                                         | 89  |

|   | 4.4.2 Experimental data                                                      | 91  |

|   | 4.5 Conclusions                                                              | 95  |

|   | 4.6 References                                                               | 96  |

|   |                                                                              |     |

| 5 | 2D nanochannel fabrication                                                   | 99  |

|   | 5.1 Nano-ridge fabrication by local oxidation of silicon edges with silicon  |     |

|   | ·                                                                            | 100 |

|   | 5.1.1 Fabrication process                                                    | 100 |

|   |                                                                              | 102 |

|   |                                                                              | 104 |

|   | 5.1.4 Nano imprint lithography using nano-ridges as a stamp                  | 105 |

|   | 5.1.5 Possible extensions of this technology                                 | 106 |

|   |                                                                              | 106 |

|   | 5.2 2D nanochannel fabrication using laser interference lithography and      |     |

|   |                                                                              | 106 |

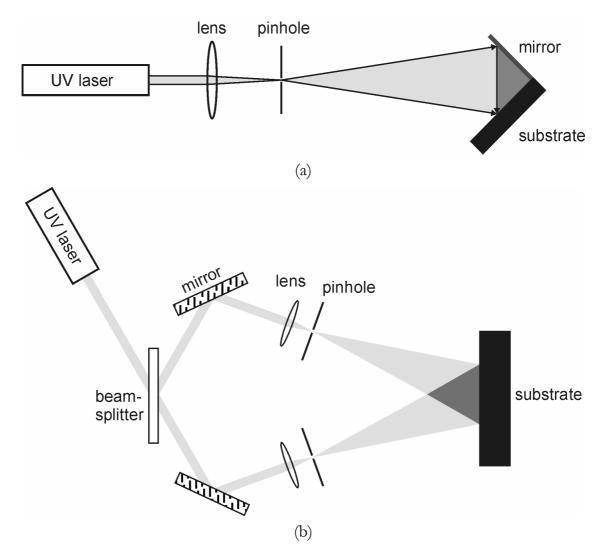

|   | <u>.</u>                                                                     | 107 |

|   |                                                                              | 109 |

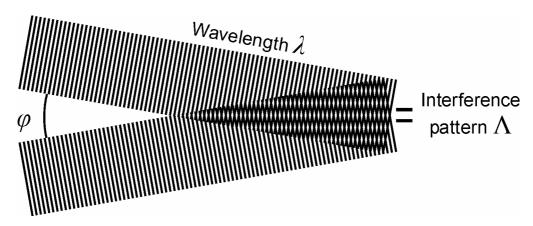

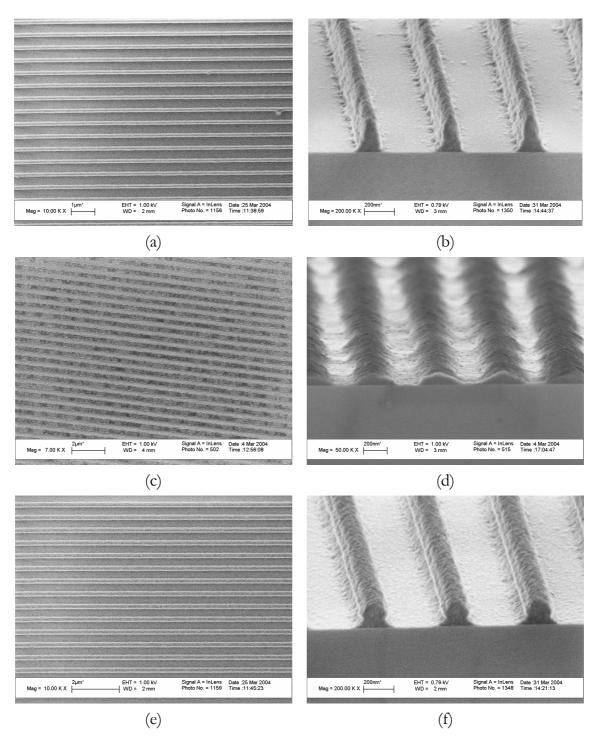

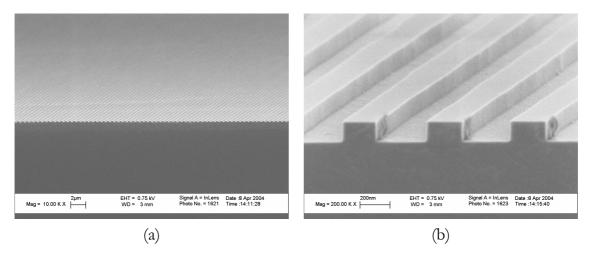

|   | 5.2.3 Pattern generation with LIL                                            | 109 |

|   |                                                                              | 112 |

|   | <u>.</u>                                                                     | 113 |

|   |                                                                              | 114 |

|   |                                                                              | 115 |

|   | 5.4 Acknowledgements                                                         | 115 |

|   | e                                                                            | 115 |

| 6  | Conclusion                     | ons and outlook                                            | 119 |

|----|--------------------------------|------------------------------------------------------------|-----|

|    | 6.1 Summ                       | ary of conclusions                                         | 120 |

|    | 6.2 Outlo                      | ok                                                         | 123 |

| A  | ppendix: F                     | Process documentation                                      | 125 |

|    | A.1 Nano                       | channel chip fabrication process                           | 126 |

|    | A.1.1                          | Mask layout and process outline                            | 126 |

|    | A.1.2                          | Top wafer processing (Borofloat)                           | 127 |

|    | A.1.3a                         | Bottom wafer processing (OPD 4262 silicon etching process) | 128 |

|    |                                | Bottom wafer processing (dry oxide spacer layer process)   | 131 |

|    | A.1.4 Direct bonding procedure |                                                            | 136 |

|    | A.2 Nano                       | -ridge fabrication process                                 | 137 |

|    | A.2.1                          | Mask layout and process outline                            | 137 |

|    | A.2.2                          | Silicon wafer processing                                   | 138 |

|    | A.3 LIL 2                      | D nanochannel fabrication process                          | 142 |

|    |                                | Mask layout and process outline                            | 142 |

|    | A.3.2                          | Silicon wafer processing                                   | 143 |

| Sı | ummary                         |                                                            | 145 |

| S  | amenvattir                     | ng                                                         | 147 |

| D  | ankwoord                       |                                                            | 149 |

# 1

# Introduction

This chapter will give an introduction into nanochannels and technologies to fabricate them. The need for developing new technologies to create nanochannels will be explained. Also, the general outline of the rest of this thesis will be discussed.

# 1.1 Nanochannels

The title of this thesis, "Nanochannel fabrication and characterization using bond micromachining", refers to the need for developing new technologies to enable us to create smaller and smaller (fluidic) channels.

In recent years, the fabrication of nanometer-sized channels and tubes has gained considerable attention because of their potential use in chemical and DNA analysis and synthesis devices [1, 2], in nanofluidic pumps [3], or as key components in very sensitive chemical sensors [4, 5]. Nanochannels can also be used for electrophoresis [6-8] or electro-osmotic flow systems [9-11]. Furthermore, they are considered very important for studies involving single molecule dynamics and fundamental research concerning the properties of fluids in these kinds of confinements.

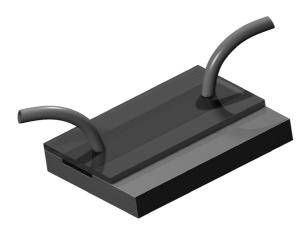

In essence, nanochannels can be divided into two categories. One-dimensional (1D) nanochannels are defined as channels having one of the dimensions (usually the depth) in the sub-micrometer range. Similarly, 2D nanochannels are channels which have both the width and the height in the nanometer range. An artist impression of a 1D nanochannel (with fluidic access tubing) can be found in Figure 1-1.

Figure 1-1: Artistic impression of a 1D fluidic nanochannel.

A lot of the applications make use of the characteristic features of nanochannels. Some of the main characteristics that separate them from microchannels are:

Large surface-volume ratio (thus a large interaction between the fluid and the channel wall).

- Electric double layer effects (see chapter 4).

- Size-effects of molecules and ions in nano-confinement (e.g.: will there be changes in the viscosity of the fluid as the channel dimensions approach the molecular dimensions?).

# 1.2 Micromachining technology as a tool for nanochannel fabrication

Micromachining is the term used to describe the fabrication of structures with micrometer-sized features, generally using silicon as a substrate material. These structures, used as sensors, actuators or fluidic systems, are often called MEMS (Micro Electro Mechanical Systems). Micromachining is based on IC technology processes: film deposition, lithography and film etching, together with additional technologies to create three-dimensional structures. Microsystems can be designed and fabricated for a wide variety of applications, for instance accelerometers in airbag systems [12-14], mechanical micro grippers [15-17], micro total analysis systems [18-20], and data storage systems [21-23]. As the race for creating smaller and smaller structures continues, a new field emerges in the form of nanotechnology, which can be described as the area of science and technology where dimensions in the range of 100 nm or smaller play a critical role. It is a multidisciplinary area of research, combining biology, materials engineering, physics, electrical and mechanical engineering to create nanosystems for information storage, single molecule detection, fuel cells, etc. In a lot of these systems, nanofluidic channels are a key element.

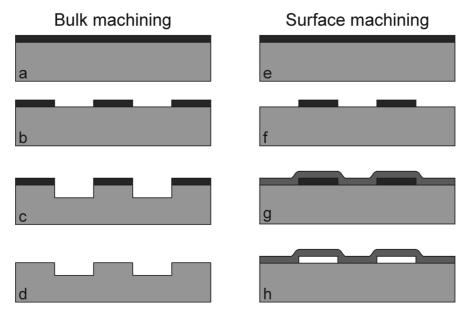

Often, the tools used in micromachining can be used in nanosystem fabrication. For overviews of silicon micro- and nanomachining technology, see [24-27]. The two main categories into which silicon machining technology can be divided are bulk machining and surface machining. Bulk machining is essentially the processing of the actual silicon bulk wafer, usually by means of dry (plasma) etching or wet anisotropic etching in basic solutions such as potassium hydroxide (KOH) or tetramethylammonium hydroxide (TMAH). Surface machining usually uses a stack of thin (100 nm-10 µm) layers which are deposited onto the silicon substrate, and then machined (by lithography, plasma etching and wet etching techniques) to

define and, if necessary, release the free standing or moveable structure. In this approach, the silicon is essentially only used to support the finished structures. For an interpretation of the difference between bulk and surface machining: see Figure 1-2. A more detailed description of the typical steps involved in both approaches will be given in the next paragraphs. In addition, bond micromachining will be discussed: a technique in which wafer bonding is used to create e.g. nanochannels.

Figure 1-2: Basic principles of bulk micromachining (left) and surface micromachining (right).

# 1.2.1 Bulk micromachining

In bulk micromachining (see Figure 1-2(a-d)), generally a mask layer (for instance silicon dioxide (SiO<sub>2</sub>), silicon nitride (SiN<sub>x</sub>), or photoresist) is deposited on a silicon substrate (a). This layer is patterned using photolithography and wet etching or dry plasma etching (b), after which it can be used as a protective layer while etching the bulk silicon (again using wet or dry etching): (c). After the silicon etching step etching the mask can (if necessary) be removed (d) and the wafer is ready for further processing.

The main two methods for the bulk etching of silicon are wet etching and dry plasma etching. These will be discussed now, together with some other technologies which are complementary. For a more thorough study on this subject, see [27].

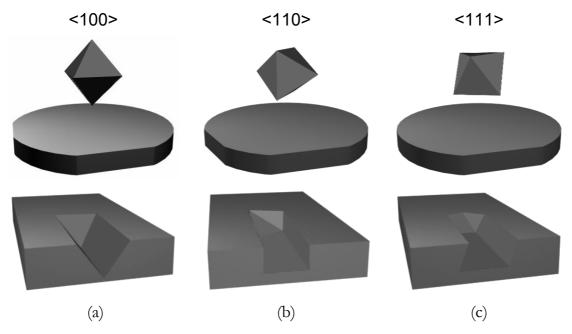

# Wet etching of silicon

Wet etching of single crystalline silicon is generally performed using basic solutions such as KOH or TMAH solutions. The advantage of this type of wet etching is that it is of anisotropic nature: the etchant etches the silicon relatively fast in the <100> and <110> directions, and virtually stops at <111> planes [28-30]. This means that well-defined structures can be created, taking the crystallographic orientation of the wafer and the mask design into account. Besides anisotropic wet etching, isotropic wet etching of silicon is also possible, using e.g. a HF:HNO<sub>3</sub> etchant [31, 32].

In Figure 1-3 the etch profiles in <100>, <110> and <111> silicon of a simple trench etched using KOH or TMAH can be seen (note: the etching of such a channel in <111> silicon is not trivial, as the wafer surface itself is <111>). The top row shows the orientation of an octahedron bound by <111> planes, relative to the orientation of the primary flat.

Figure 1-3: Orientation dependent (anisotropic) wet etching profiles for (a): <100>, (b): <110>, and (c): <111> oriented silicon wafers etched in alkaline solutions. Top row: position of the octahedron limited by <111> planes relative to the wafer flat (can depend on supplier). Bottom row: cross-section of the final structure after etching a trench, aligned parallel to the primary flat of the wafer.

If the <100> wafer was to be etched for a long period of time, the resulting structure would be a V-groove (the angle at which the <111> planes intersect the surface with an angle of 54.7 degrees). For shorter etch durations the channel

bottom is flat and the sidewalls are slanted. In contrast to this, the <110> wafer is able to provide trenches with (near-)vertical sidewalls, due to the fact that the <111> planes are positioned perpendicular to the wafer surface. The only factor limiting this is the selectivity between the etch rate of the <110> and <111> planes: this varies with the etchant used, and can be as high as 400:1 [27].

# Dry etching of silicon

As an alternative to wet anisotropic silicon etching, dry plasma etching (or reactive ion etching: RIE) can be used to create structures in silicon (or films deposited on silicon) [24, 33-35]. In plasma etching, molecules are dissociated and ionized. Part of the chemically reactive species takes part in isotropic etching of the substrate, while others have a passivating function. The ions are accelerated perpendicularly to the wafer surface and physically bombard the substrate, thereby locally removing the passivation and allowing the reactive species to etch the substrate. This results in directional etching, because the passivation is only removed at the bottom of the structures (ion impact), and not at the side-walls (no ion impact). The balance between the isotropic and directional etching, together with the passivation, ultimately determines the geometry of the side-wall of the structure.

One of the advantages of RIE is that often a normal photoresist mask can be used as an etch mask, whereas in wet etching generally a dedicated mask layer (often silicon dioxide or silicon nitride) is needed, because the often very alkaline solutions effectively act as a photoresist stripping solution. There are numerous amounts of different dry etching recipes, all having different etch speeds and profiles, ranging from very anisotropic to totally isotropic [36]. The profile of the final structure depends on the process parameters used.

# Other bulk etching technologies

Another way to etch bulk silicon (or glass) is powder blasting (also called sand blasting, or abrasive jet machining) [37]. This technique uses pressurized air to accelerate ceramic particles (with a size of 3 to 30 µm) towards a substrate which is masked with a patterned photosensitive rubber foil. The main advantage of this technology is the very high etch speed which can be obtained. A downside to the process is that the surface finish is rather rough after etching, and that the smallest

possible trench width which can be etched is around 10 µm. Powder blasting is routinely used to create access holes in silicon and glass wafers.

Focused ion beam milling [38] can also be used to remove bulk material. It provides very high resolution (< 50 nm), but lacks processing speed because the pattern is directly "written" into the substrate.

The same goes for laser machining [24], which has a lower resolution of 1 micrometer and is sometimes used for drilling holes in silicon wafers, and to scribe ID codes on wafers.

# 1.2.2 Surface micromachining

In surface machining (see Figure 1-2(e-h), [24, 39]) structures are fabricated by first depositing a sacrificial or spacer layer (or multiple layers) on a silicon substrate (e), patterning this layer (f) and then depositing a conformal capping layer (g). Then, the sacrificial layer is removed by creating access holes in the capping layer (usually by plasma etching) and subsequent etching with a wet chemical etchant, or an isotropic plasma etch step (h). One of the critical steps is this sacrificial etch step: often this step takes a substantial amount of time, because of the fact that the sacrificial layer is etched laterally (instead of perpendicular to the surface). This means that the selectivity between the sacrificial layer and its adjacent materials is a crucial factor in surface micromachining. If the selectivity is too low, excessive tapering of the channel height will occur. Other important factors are film thickness, uniformity and stress in the deposited layers. Furthermore, attention must be paid to prevent stiction of the capping layer to the substrate during release [40, 41]. Because the layers are thin and surface areas relatively large, the membranes can deflect rather easily. When the wafer is dried after wet etching of the sacrificial layer, the surface tension of the liquid pulls the structure towards the substrate, to which it can permanently adhere ("stiction"). To prevent stiction, e.g. freeze drying can be used.

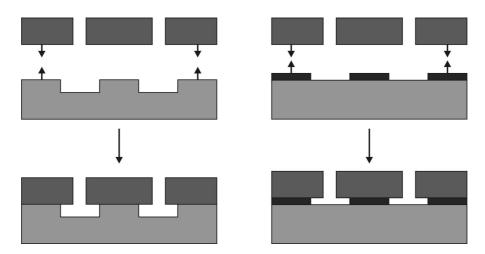

# 1.2.3 Bond micromachining

The term bond micromachining refers to a technology to create sealed (nano)channels, using wafer bonding to seal the device. A patterned wafer with the channel structures (e.g. fabricated by bulk etching of silicon, or by surface machining of a spacer layer) is bonded to a cover wafer (usually silicon or glass), using direct bonding or anodic bonding. The cover wafer can have pre-fabricated

access holes, for fluidic connectivity. For wafer bonding very smooth surfaces are required (especially in the case of direct bonding).

**Figure 1-4:** Principle of bond micromachining. Left: based on bulk etching of silicon and wafer bonding. Right: based on surface machining and bonding.

The main advantage of this technology, when compared to for instance sacrificial etching of channels, is the ease of fabrication (no time consuming sacrificial etch step is needed), and the uniformity of the depth of the channels which can be obtained (when using sacrificial etching the channel height is often tapered due to limited etching selectivity between the sacrificial layer and the surrounding channel wall material. Bond micromachining will be the main technique to fabricate nanochannels throughout this thesis.

# 1.3 Applications of nanochannels

Although it is impossible to give a complete overview of the wide range of applications in which nanochannels are or can be used, some characteristic ones are mentioned in more detail below.

Han and Craighead [2, 42] demonstrated the separation of long DNA molecules in an entropic trap array, fabricated by standard silicon micromachining technology. Deep (1.5-3 µm) trenches are interconnected by 1D nanochannels with a height ranging from 75 to 100 nm. The structures are created in two RIE steps: the first defining the nanochannels, the second creating the deeper trenches. The etched wafer is then bonded to a Pyrex cover wafer. During the separation experiments,

initially the DNA molecules are trapped in a deep region, because their radius of gyration is much larger than the height of the nanochannels. The DNA is then separated by applying a DC field, creating electrophoretic mobility differences. The molecules can slip through a nanochannel because they are able to change their confirmation. Interestingly, large DNA molecules have a higher escape probability than small ones (because they have a larger contact area with the interface between a deep region and a connecting nanochannel, they also have a higher "escape attempt frequency").

Another examples of size separation of DNA or other large molecules is given by Chou et al. [8]. In their device, consisting of a 350 nm high channel with a two-dimensional lattice of obstacles with asymmetric disposition, the Brownian motion of large molecules (e.g. DNA) is rectified, so that the molecules follow different paths through the structure, depending on their diffusion coefficient (and thus on their size). They have achieved a 6% resolution in length of DNA molecules (in the size range of 15-30 kbp) on a 100 mm wafer scale.

An example of a nanofluidic pumping device is demonstrated by Tas et al. [3]. A sacrificial layer technique is used to create a bubble pump with a "reservoir" which fills by capillary forces, after which the liquid is forced out by applying air pressure. After ejection of the liquid, the air pressure is dropped, and the device fills by capillary force again. Reproducible dispensing of droplets of 40 pL of water has been achieved using this type of device.

Karlsson et al. [43, 44] used confocal laser induced fluorescence to detect single 30 nm-sized beads flowing through lipid nanotubes. The nanotubes have an inner diameter between 100 and 300 nm and a wall thickness of approximately 5 nm. They are drawn from the lipid bilayer of a vesicle by means of a micropipette.

# 1.4 Fabrication technologies for nanochannels

To give the reader an idea of which technologies are currently used to fabricate nanochannels, some typical examples are treated in this paragraph.

An example of using sacrificial materials, in this case polymers, to create nanofluidic channels, is given by Li et al. [45]. A polynorbornene (PNB) layer is spun onto a

silicon substrate, and is then patterned using standard photolithography, followed by reactive ion etching of the PNB layer. A capping layer (silicon dioxide, silicon nitride or polyimide) is conformally deposited, after which the PNB layer is removed by thermo-decomposition at a temperature of 425°C, leaving channels with a height ranging from 40 µm to 100 nm.

Eijkel et al. [46] use a somewhat similar method, although they use aluminum as a sacrificial layer to form all-polyimide 1D nanochannels. First a layer of polyimide is spin coated on a silicon substrate, then a 100 or 500 nm thick layer of aluminum is sputter deposited, and patterned using standard photolithography and wet etching of aluminum. Subsequently a second layer of polyimide is spin coated and patterned using UV exposure and development. After curing the polyimide layer, the aluminum is etched during 20 hours in aluminum etchant. Capillary filling with water, isopropanol and ethanol was demonstrated. The 500 nm deep channels all filled readily with the fluids, however for the 100 nm deep channels the filling could only be performed for channel widths up to 5 μm. Wider channels appeared to collapse during the drying process at the end of the fabrication sequence.

Foquet [1] demonstrates a sacrificial method to fabricate channels, which can later be used for DNA fragment sizing. On a fused silica substrate, a 300 nm layer of polysilicon is deposited, which is patterned to leave the intended channel structure. The whole wafer is then capped with a 1 µm thick layer of fused silica, and after creating access holes, the polysilicon sacrificial layer is removed by etching in 5% TMAH at 75°C, for a period of 4 hours. Stern et al. have developed a similar technology to fabricate nanochannels for chemical sensors [4], using a 20-100 nm thick layer of amorphous silicon as the sacrificial layer, and stoichiometric silicon nitride (Si<sub>3</sub>N<sub>4</sub>) as the capping layer.

Recently, Kutchoukov et al. [47] have used reactive ion etching of glass to create 1D nanochannels in Borofloat glass wafers: a 33 nm thick amorphous silicon layer is patterned and used as a RIE mask to etch channels in the glass wafer. The channel depth is defined by the etching time, and consists of the thickness of the amorphous silicon layer, plus the glass etch depth. After etching the wafers are bonded anodically.

The same principle has been used by Kameoka and Craighead [5] to fabricate a refractive index sensor using photon tunneling in a nanofluidic channel.

Mao et. al. [48] fabricated planar nanofluidic channels (similar to Figure 1-1) using reactive ion etching of silicon and anodic bonding to a glass wafer, or by wet etching of Pyrex or Borofloat glass using buffered oxide etchant, and subsequent direct bonding to another glass wafer. The authors report channel collapse when using anodic bonding in combination with low channel depth and high channel width (20 nm  $\times$  10  $\mu$ m, 40 nm  $\times$  20  $\mu$ m).

A demonstration of the fabrication of self-sealing, flexible, polymer nanochannels is given by Ilic et al. [6]. First a silicon mold is fabricated, containing trenches with a width between 400 nm and 20 µm, and a height ranging from 2 to 20 µm. Then, vapor deposition of parylene is used to seal the channels. The non-conformal step coverage associated with his deposition process forms flexible parylene nanotubes inside the trenches, with an inner diameter in the 100 nm regime. Capillary and electrophoretic driven flow was demonstrated in capillaries up to 5 cm in length. A drawback of this technique is that it is difficult to gain complete control over the inner dimensions of the resulting nanotubes.

Another method to create nanochannels (in this particular case two-dimensional) is fast atom beam etching, employed by Hibara [49]. Nanochannel patterns were defined in a resist layer using E-beam lithography. The resist pattern is then transferred to the underlying silicon substrate in an atom beam etcher. In this machine CHF<sub>3</sub> gas is first ionized, then accelerated by a high voltage, and finally neutralized, before hitting the substrate with atom velocities around 100 km/s. This way, 330 nm and 850 nm sized channels were fabricated. The authors also performed filling of the channels with water and fluorescent solutions. A noticeable filling speed reduction was observed in the 330 nm sized channels (the mean velocity was four times slower than expected).

## 1.5 Aim of this thesis

The continuously growing interest in artificial nanostructures has stimulated the search for novel nanofabrication techniques. All mentioned techniques to construct nanochannels have some drawbacks. The surface nanomachining method is rather

complex and, unless special access holes are used, long etch times are needed to remove the sacrificial layer completely. In this case the selectivity between sacrificial and capping layer is also of importance, because it will ultimately determine the amount of tapering in the channel height. The mentioned bulk and bond machining techniques usually make use of expensive RIE equipment and special masks for pattern transfer. RIE normally creates rough surfaces and the sidewalls of the trench can be tapered. Especially when the width of the trench is in the same order of magnitude as the trench depth (i.e. sub-100 nm), the roughness and shape of the sidewalls will have a major influence on the flow characteristics of the nanochannel.

This thesis will primarily deal with the development of simple and robust, yet highly accurate processes for the fabrication of 1D fluidic nanochannels. Key aspects are reducing the channel depth (below 100 nm), while keeping accurate control over it, and smooth surface finish (the channel walls, top and bottom surfaces should have very low roughness). Furthermore characterization methods (channel depth measurement) have to be addressed. Finally, ease of fabrication is an important factor: eliminating the use of expensive RIE equipment and complex and time-consuming sacrificial etch methods can cut costs and time. A step further will also be taken into the area of two-dimensional nanochannel fabrication.

Not only fabrication technology will be discussed, but also the filling behavior of fluids in nanochannels has to be studied and compared to a theoretical model.

# 1.6 Thesis outline

The second chapter deals with the development of a basic process flow for the creation of 1D fluidic nanochannels. Two possible approaches are discussed: anisotropic wet etching of bulk silicon and subsequent bonding, and the surface machining method of depositing and selectively etching of a spacer layer, followed by bonding. The various characteristics, advantages and limitations of both processes will be discussed, leaving us with a nanochannel fabrication "toolbox". In the third chapter, the creation of nanofluidic chips, with interfacing to the environment will be treated. This will involve nanochannel fabrication, as described in chapter two, but also the creation of microfluidic reservoirs, measurement rulers on the chip, and bonding of the silicon wafers to Borofloat glass wafers, which have pre-fabricated access holes to enable fluid injection.

After the fabrication of complete chips, they are analyzed in chapter four: various liquids will be introduced into the chips by means of capillary filling. A model for the filling speed will be developed, based on the classical Washburn theory, and the actual filling speed of the channels will be determined using optical microscopy, in combination with a digital video camera. The theoretical and experimental values for the filling speed will be compared.

Taking nanochannel fabrication one step further, in chapter five some first steps are taken to fabricate two dimensional nanochannels. Two possible ways are suggested. The first is via the use of local oxidation of silicon (an edge lithography method), in combination with nano imprint lithography. The second one is by directly creating channels with sub-micrometer width and depth by using laser interference lithography in combination with wet anisotropic etching of silicon, using the same process as in chapter three.

Finally, chapter six will consist of a detailed overview of the main conclusions of this thesis and recommendations for future research.

# 1.7 References

- [1] M. Foquet, J. Korlach, W. Zipfel, W. W. Webb, and H. G. Craighead, "DNA fragment sizing by single molecule detection in submicrometer-sized closed fluidic channels," *Analytical Chemistry*, vol. 74, pp. 1415-1422, 2002.

- [2] J. Han and H. G. Craighead, "Separation of long DNA molecules in a microfabricated entropic trap array," *Science*, vol. 288, pp. 1026-1029, 2000.

- [3] N. R. Tas, J. W. Berenschot, T. S. J. Lammerink, M. Elwenspoek, and A. Van den Berg, "Nanofluidic bubble pump using surface tension directed gas injection," *Analytical Chemistry*, vol. 74, pp. 2224-2227, 2002.

- [4] M. B. Stern, M. W. Geis, and J. E. Curtin, "Nanochannel fabrication for chemical sensors," *Journal of Vacuum Science & Technology B (Microelectronics and Nanometer Structures)*, vol. 15, pp. 2887-91, 1997.

- [5] J. Kameoka and H. G. Craighead, "Nanofabricated refractive index sensor based on photon tunneling in nanofluidic channel," *Sensors and Actuators, B: Chemical*, vol. 77, pp. 632-637, 2001.

- [6] B. Ilic, D. Czaplewski, M. Zalalutdinov, B. Schmidt, and H. G. Craighead, "Fabrication of flexible polymer tubes for micro and nanofluidic applications," *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures*, vol. 20, pp. 2459-2465, 2002.

- [7] S. W. Turner, A. M. Perez, A. Lopez, and H. G. Craighead, "Monolithic nanofluid sieving structures for DNA manipulation," *Journal of Vacuum Science*

- & Technology B (Microelectronics and Nanometer Structures), vol. 16, pp. 3835-40, 1998.

- [8] C. F. Chou, O. Bakajin, S. S. Chan, R. H. Austin, E. C. Cox, S. W. P. Turner, H. G. Craighead, and T. A. J. Duke, "Sorting by diffusion: An asymmetric obstacle course for continuous molecular separation," *Proceedings of the National Academy of Sciences of the United States of America*, vol. 96, pp. 13762-13765, 1999.

- [9] R. Qiao and N. R. Aluru, "Charge inversion and flow reversal in a nanochannel electro-osmotic flow," *Physical Review Letters*, vol. 92, pp. 198301-1, 2004.

- [10] Z. Zheng, D. J. Hansford, and A. T. Conlisk, "Effect of multivalent ions on electroosmotic flow in micro- and nanochannels," *Electrophoresis*, vol. 24, pp. 3006-3017, 2003.

- [11] S. C. Jacobson, J. P. Alarie, and J. M. Ramsey, "Electrokinetic transport through nanometer deep channels," *Proc. Micro Total Analysis Systems 2001, Monterey, USA*, pp. 57-59, 2001.

- [12] W. Kuehnel and S. Sherman, "Surface micromachined silicon accelerometer with on-chip detection circuitry," *Sensors and Actuators, A: Physical*, vol. 45, pp. 7-16, 1994.

- [13] L. Zimmermann, J. P. Ebersohl, F. Le Hung, J. P. Berry, F. Baillieu, P. Rey, B. Diem, S. Renard, and P. Caillat, "Airbag application: A microsystem including a silicon capacitive accelerometer, CMOS switched capacitor electronics and true self-test capability," *Sensors and Actuators, A: Physical*, vol. 46, pp. 190-195, 1995.

- [14] K. H. Kim, J. S. Ko, Y.-H. Cho, K. Lee, B. M. Kwak, and K. Park, "Skew-symmetric cantilever accelerometer for automotive airbag applications," *Sensors and Actuators, A: Physical*, vol. 50, pp. 121-126, 1995.

- [15] C. S. Pan and W. Hsu, "An electro-thermally and laterally driven polysilicon microactuator," *Journal of Micromechanics and Microengineering*, vol. 7, pp. 7-13, 1997.

- [16] C.-J. Kim, A. P. Pisano, R. S. Muller, and M. G. Lim, "Polysilicon microgripper," *Sensors and Actuators, A: Physical*, vol. 33, pp. 221-227, 1992.

- [17] I. Roch, P. Bidaud, D. Collard, and L. Buchaillot, "Fabrication and characterization of an SU-8 gripper actuated by a shape memory alloy thin film," *Journal of Micromechanics and Microengineering*, vol. 13, pp. 330-336, 2003.

- [18] D. R. Reyes, D. Iossifidis, P. A. Auroux, and A. Manz, "Micro total analysis systems. 1. Introduction, theory, and technology," *Analytical Chemistry*, vol. 74, pp. 2623-2636, 2002.

- [19] P. A. Auroux, D. Iossifidis, D. R. Reyes, and A. Manz, "Micro total analysis systems. 2. Analytical standard operations and applications," *Analytical Chemistry*, vol. 74, pp. 2637-2652, 2002.

- [20] T. Vilkner, D. Janazek, and A. Manz, "Micro total analysis systems. Recent developments," *Analytical Chemistry*, vol. 76, pp. 3373-3386, 2004.

- [21] E. Eleftheriou, T. Antonakopoulos, G. K. Binnig, G. Cherubini, M. Despont, A. Dholakia, U. Durig, M. A. Lantz, H. Pozidis, H. E. Rothuizen, and P.

- Vettiger, "Millipede a MEMS-based scanning-probe data-storage system," *IEEE Transactions on Magnetics*, vol. 39, pp. 938-945, 2003.

- [22] P. Vettiger, M. Despont, U. Drechsler, U. Dürig, W. Häberle, M. I. Lutwyche, H. E. Rothuizen, R. Stutz, R. Widmer, and G. K. Binnig, "`Millipede' more than one thousand tips for future AFM data storage," *IBM Journal of Research and Development*, vol. 44, pp. 323-340, 2000.

- [23] M. I. Lutwyche, M. Despont, U. Drechsler, U. Dürig, W. Häberle, H. Rothuizen, R. Stutz, R. Widmer, G. K. Binnig, and P. Vettiger, "Highly parallel data storage system based on scanning probe arrays," *Applied Physics Letters*, vol. 77, pp. 3299-3301, 2000.

- [24] M. J. Madou, Fundamentals of microfabrication. CRC-Press, Boca Raton, 1998.

- [25] A. t. Wolde, Nanotechnology: towards a molecular construction kit. The Hague: STT, 1998.

- [26] M. Elwenspoek and H. Jansen, *Silicon micromachining*. Cambridge University Press, Cambridge, 1998.

- [27] H. V. Jansen, N. R. Tas, and J. W. Berenschot, "MEMS-Based Nanotechnology," *Encyclopedia of Nanoscience and Nanotechnology*, vol. 5, pp. 163-275, 2004.

- [28] M. Vangbo and Y. Bäcklund, "Precise mask alignment to the crystallographic orientation of silicon wafers using wet anisotropic etching," *Journal of Micromechanics and Microengineering*, vol. 6, pp. 279-284, 1996.

- [29] H. Seidel, L. Csepregi, A. Heuberger, and H. Baumgaertel, "Anisotropic etching of crystalline silicon in alkaline solutions. I. Orientation dependence and behavior of passivation layers," *Journal of the Electrochemical Society*, vol. 137, pp. 3612-3626, 1990.

- [30] A. J. Nijdam, "Anisotropic wet-chemical etching of silicon: pits, peaks, principles, pyramids and particles," Ph.D. Thesis, University of Twente, Enschede, 2001.

- [31] R. W. Tjerkstra, "Isotropic etching of silicon in fluoride containing solutions as a tool for micromachining," Ph.D. Thesis, University of Twente, Enschede, 1999.

- [32] D. L. Klein and D. J. D'Stefan, "Controlled etching of silicon in the HF-HNO<sub>3</sub> system," *Journal of the Electrochemical Society*, vol. 109, pp. 37-42, 1962.

- [33] M. J. de Boer, J. W. Berenschot, J. G. E. Gardeniers, M. Elwenspoek, A. Van Den Berg, R. W. Tjerkstra, H. V. Jansen, and G. J. Burger, "Micromachining of buried micro channels in silicon," *Journal of Microelectromechanical Systems*, vol. 9, pp. 94-103, 2000.

- [34] G. T. A. Kovacs, N. I. Maluf, and K. E. Petersen, "Bulk micromachining of silicon," *Proceedings of the IEEE*, vol. 86, pp. 1536-1551, 1998.

- [35] H. Jansen, M. de Boer, R. Legtenberg, and M. Elwenspoek, "Black silicon method: a universal method for determining the parameter setting of a fluorine-based reactive ion etcher in deep silicon trench etching with profile control," *Journal of Micromechanics and Microengineering*, vol. 5, pp. 115-120, 1995.

[36] M. J. De Boer, J. G. E. Gardeniers, H. V. Jansen, E. Smulders, M. J. Gilde, G. Roelofs, J. N. Sasserath, and M. Elwenspoek, "Guidelines for etching silicon MEMS structures using fluorine high-density plasmas at cryogenic temperatures," *Journal of Microelectromechanical Systems*, vol. 11, pp. 385-401, 2002.

- [37] H. Wensink, "Fabrication of Microstructures by Powder Blasting," Ph.D. Thesis, University of Twente, Enschede, 2002.

- [38] S. Reyntjens and R. Puers, "A review of focused ion beam applications in microsystem technology," *Journal of Micromechanics and Microengineering*, pp. 287-300, 2001.

- [39] J. M. Bustillo, R. T. Howe, and R. S. Muller, "Surface micromachining for microelectromechanical systems," *Proceedings of the IEEE*, vol. 86, pp. 1552-1574, 1998.

- [40] C. H. Mastrangelo and C. H. Hsu, "Mechanical stability and adhesion of microstructures under capillary forces. I. Basic theory," *Journal of Microelectromechanical Systems*, vol. 2, pp. 33-43, 1993.

- [41] C. H. Mastrangelo and C. H. Hsu, "Mechanical stability and adhesion of microstructures under capillary forces. II. Experiments," *Journal of Microelectromechanical Systems*, vol. 2, pp. 44-55, 1993.

- [42] J. Han and H. G. Craighead, "Entropic trapping and sieving of long DNA molecules in a nanofluidic channel," *Journal of Vacuum Science & Technology A Vacuum Surfaces and Films*, vol. 17, pp. 2142-2147, 1999.

- [43] A. Karlsson, M. Karlsson, R. Karlsson, K. Sott, A. Lundqvist, M. Tokarz, and O. Orwar, "Nanofluidic networks based on surfactant membrane technology," *Analytical Chemistry*, vol. 75, pp. 2529-2537, 2003.

- [44] R. Karlsson, A. Karlsson, and O. Orwar, "A nanofluidic switching device," *Journal of the American Chemical Society*, vol. 125, pp. 8442-8443, 2003.

- [45] W. Li, J. O. Tegenfeldt, L. Chen, R. H. Austin, S. Y. Chou, P. A. Kohl, J. Krotine, and J. C. Sturm, "Sacrificial polymers for nanofluidic channels in biological applications," *Nanotechnology*, vol. 14, pp. 578-583, 2003.

- [46] J. C. T. Eijkel, J. Bomer, N. R. Tas, and A. van den Berg, "1-D nanochannels fabricated in polyimide," *Lab on a Chip*, vol. 4, pp. 161-163, 2004.

- [47] V. G. Kutchoukov, F. Laugere, W. van der Vlist, L. Pakula, Y. Garini, and A. Bossche, "Fabrication of nanofluidic devices using glass-to-glass anodic bonding," *Sensors and Actuators A (Physical)*, vol. 114, pp. 521-527, 2004.

- [48] P. Mao and J. Han, "Fabrication and characterization of 20 nm planar nanofluidic channels by glass-glass and glass-silicon bonding," *Lab on a Chip Miniaturisation for Chemistry and Biology*, vol. 5, pp. 837-844, 2005.

- [49] A. Hibara, T. Saito, H. B. Kim, M. Tokeshi, T. Ooi, M. Nakao, and T. Kitamori, "Nanochannels on a fused-silica microchip and liquid properties investigation by time-resolved fluorescence measurements," *Analytical Chemistry*, vol. 74, pp. 6170-6176, 2002.

# Fabrication of 1D nanochannels\*

This chapter deals with the issues concerning the fabrication of 1D fluidic nanochannels. Two possible technologies are described and developed: one where the channels are etched using wet anisotropic etching of <110> silicon wafers (bulk machining), and one where the channel is formed by selectively etching of a well defined oxide layer (surface machining). Both methodologies have their own characteristics, advantages and disadvantages, which will be discussed.

<sup>\*</sup> In this chapter, the paragraphs involving wet anisotropic etching of <110> silicon are based on: J. Haneveld, H. Jansen, E. Berenschot, N. Tas, and M. Elwenspoek, "Wet anisotropic etching for fluidic 1D nanochannels," *Journal of Micromechanics and Microengineering*, vol. 13, pp. 62-66, 2003.

# 2.1 Wet anisotropic etching of <110> silicon for 1D fluidic nanochannels

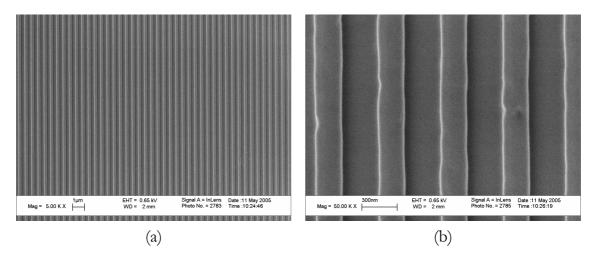

Standard technologies to etch channels [1, 2] with nanometer depth, all suffer from one or more drawbacks. RIE, for instance, can produce channels with submicrometer depth in silicon [3] or in glass [4], but the exact channel depth is not easily controlled, because the etch rate is generally considerably high. Also, RIE can leave a rough surface finish and, depending on the process parameters, tapered sidewalls. To be able to etch fluidic 1D channels with a well defined and controlled geometry, a process was developed, which uses wet anisotropic etching of silicon by TMAH, in combination with <110> wafers, giving the possibility to create channels with rectangular cross-sections. This also simplifies the modeling of fluid behavior in these channels. Moreover, due to the low lateral etch rate, control over the line width is excellent. This is of importance when the width of the channels is also reduced to sub-micrometers.

## 2.1.1 Etchant selection

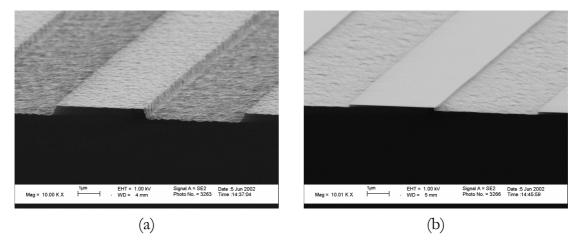

As stated before, for nanofluidic applications (using channels with a depth below 100 nm) it is important that the etch depth is well controlled and the surface roughness is minimized. The etch rate of the etchant should be low enough to allow for accurate etch depth control, but also high enough to be of practical use. To reduce roughness, the addition of additives such as surfactants is an option [5, 6]. To select the best wet etchant for creating sub-100 nm channels, 2.5% KOH, NaOH and TMAH solutions were investigated. Samples etched in aqueous KOH, NaOH and TMAH clearly showed a roughened surface after the etching process. A separate fourth sample, etched in Olin OPD 4262 developer (Arch Chemicals, containing 2.5% TMAH and a number of surfactants), had a very smooth finish after etching. The smooth surface in comparison to the samples etched in a standard 2.5% TMAH solution must be caused by the addition of the surfactants to the OPD 4262 solution. However, the addition of surfactants does not necessarily have such a big positive effect, as was proven in a test with a 5% NaOH solution versus Clariant AZ 351B NaOH developer, which also contains 5% NaOH (see Figure 2-1). The surface roughness did improve due to the additives in the

developer, but the resulting surface was still far from being as smooth as that of the samples etched in OPD 4262.

**Figure 2-1:** Effect of surfactant addition to NaOH solution. (a) <110> silicon, etched for 15 minutes in a 5% NaOH solution. (b) Etched in a Clariant AZ 351B NaOH developer diluted to 5% NaOH content. Note that the surface finish improves, and that the etch rate decreases.

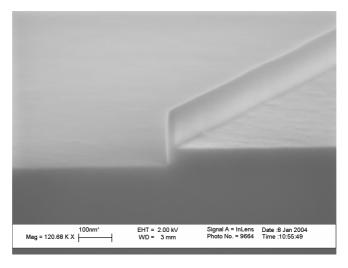

An example of a <110> silicon wafer, etched in OPD 4262, can be found in Figure 2-2. The surface finish of the bottom of the trench is by far superior to all other candidates, and roughness could not be observed by high resolution scanning electron microscopy.

Figure 2-2: <110> silicon etched in OPD 4262 developer. Notice the straight and vertical sidewalls, as well as the extremely smooth surface at the bottom of the trench. The step height was determined to be 335 nm.

## 2.1.2 Mask material selection

Normally, when using wet bulk etching of silicon in alkaline solutions (generally KOH), a mask layer is deposited on the substrate. This is generally a layer of silicon dioxide (SiO<sub>2</sub>) or silicon nitride (SiN<sub>x</sub>). In the next step of the process this layer is patterned using photolithography and wet or dry etching of the mask layer. The resulting patterned mask layer is then used as an etch mask for the actual etching of the silicon wafer. For this, it is useful that the ratio of the etch rates of silicon and silicon dioxide (or nitride) is very high, as can be seen in Table 2-I. The selectivity for silicon and silicon nitride is even 30 times better.

| Material                        | Etch rate in 25% KOH @ 75°C | Selectivity towards <100> |

|---------------------------------|-----------------------------|---------------------------|

| Si <100>                        | 60 μm/hour                  | 1                         |

| Si <110>                        | 100 μm/hour                 | 0.6                       |

| Si <111>                        | 0.75 μm/hour                | 80                        |

| SiO <sub>2</sub> (thermal)      | 0.18 μm/hour                | $3.10^{2}$                |

| SiN <sub>x</sub> (silicon rich) | <0.006 μm/hour              | 1·10 <sup>4</sup>         |

**Table 2-I:** Etch rate comparison of silicon and mask materials in a standard KOH solution [7].

From these values we can estimate the oxide thickness that would be necessary to etch channels with a depth up to 500 nm, using thermal oxide as a mask and 25% KOH at 75°C as the etchant. The required SiO<sub>2</sub> thickness is 500·0.18/60 = 1.5 nm. The native oxide layer, which is always present on a silicon wafer due to cleaning in HNO<sub>3</sub>, Piranha solution or spontaneous oxidation in air, has a thickness which is normally assumed to be between 0.5 and 2 nm [8]. In our case the selectivity between silicon <110> and native oxide may be different than the one based on the values in Table 2-I, because instead of KOH we use OPD 4262 as an etchant, at room temperature. Still, the native oxide might provide a sufficiently thick mask to etch nanochannels without the need of depositing a dedicated mask first. A proposed nanochannel fabrication process, including an etch rate determination and calibration, will be discussed in the following paragraphs.

# 2.1.3 Basic fabrication process

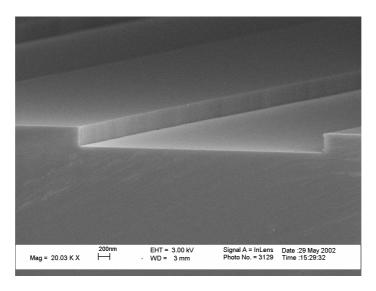

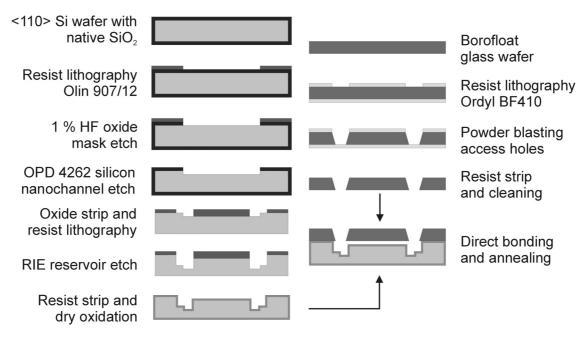

The proposed basic process for creating and sealing 1D fluidic nanochannels in <110> silicon, using native oxide as a mask material, is depicted in Figure 2-3.

Figure 2-3: Basic process for the fabrication of nanochannels using wet anisotropic etching of <110> silicon.

# Lithography

A <110> p-type silicon wafer is used in the experiments. Using this wafer, the following lithographic steps are performed: after a dehydration step (>10 min at 120°C), an adhesion layer (HMDS: HexaMethylDiSilizane) and photosensitive resist (Olin 907/12) are subsequently spin-coated (20 seconds at 4000 rpm). Then, after a softbake (1 min at 95°C), the resist is exposed (4 sec at 12 mW/cm²) using an ElectroVisions 620 exposure apparatus (EVG), and a mask containing 4 μm wide lines and spacings. After this, a post exposure bake (1 min at 120°C) is performed followed by development of the exposed resist by a standard 2.5% water diluted TMAH solution (Olin OPD 4262).

# Pattern transfer to native oxide layer

After lithography, a 1% HF dip (1 min) is done to transfer the resist pattern to the native oxide layer. This is rather longer than the time which is necessary to remove the native oxide layer (approximately 20 seconds). The reason for this generous overetch is to be absolutely sure that all of the oxide is removed for the etching process. Then the wafer is immersed in acetone for one minute to strip the resist, directly followed by an isopropanol (IPA) cleaning dip (1 min), after which the wafer is blow-dried with nitrogen gas. The reason for the use of the IPA dip is that it removes the acetone (together with any dissolved photoresist) from the surface of the wafer before the drying. IPA also leaves a much cleaner surface than acetone when blow-drying (no streaks or spots on the wafer).

# Anisotropic wet etching of silicon

The pattern transfer into the native oxide is directly followed by a silicon etch at room temperature using a fresh OPD 4262 solution as the wet chemical etchant and the native oxide as the mask material. Finally, the wafer is rinsed with DI water and spin-dried.

# Channel depth measurement

After a surface scan with a mechanical profiler (Sloan Dektak II) to determine the depth of the silicon nanochannels, the wafer together with a cover wafer is ready for bonding or further processing of the wafer.

# 2.1.4 Etch rate calibration of silicon in OPD 4262 developer

To determine the usability of OPD 4262 as an etchant for creating 1D fluidic nanochannels, the etch rates of different silicon orientations were determined, as well as the influence of diluting the OPD 4262 solution, to be able to etch at various etch rates, depending on the desired channel depth.

# Etch rate of silicon in OPD 4262

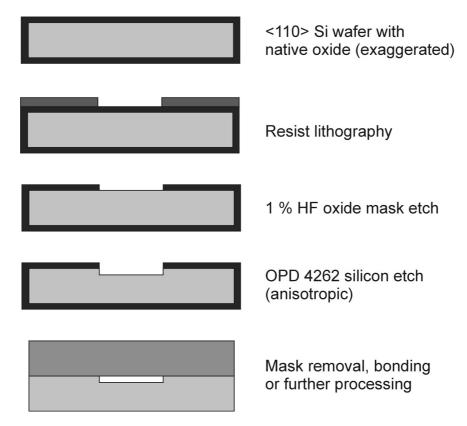

First, a calibration of the etch rate of silicon in pure OPD 4262 developer was performed to be able to predict the necessary etching time for a given channel depth. To accomplish this, the procedure of Figure 2-3 was used, with etch times up to 300 minutes. The etch rates of p-type silicon <100>, <110> and <111>

oriented wafers were determined to estimate the selectivity of the various orientations relative to each other. The channel depths were measured using a Dektak profilometer. The graph of the channel depth versus the time can be found in Figure 2-4.

Figure 2-4: Etch rates for silicon <100>, <110> and <111> in OPD 4262 positive resist developer at room temperature.

From this graph some important conclusions can be drawn. The first is that OPD 4262 developer etches <110> silicon with a speed of 3.7 nm/min (220 nm/hr) at room temperature. This is a very convenient speed when aiming for nanochannels in the sub-500 nm range. The etch rates for all three silicon orientations can be found in Table 2-II.

| Material | Etch rate in OPD 4262 @ room-T |

|----------|--------------------------------|

| Si <100> | 3.8 nm/min = 230 nm/hr         |

| Si <110> | 3.7 nm/min = 220 nm/hr         |

| Si <111> | 0.8  nm/min = 50  nm/hr        |

Table 2-II: Etch rate comparison of silicon <100>, <110> and <111> in OPD 4262 developer.

Another observation is that the maximum channel depth which can be produced using this method is approximately 500 nm. At longer etching times (above 200 minutes) the channel depth does not increase any further. This is most likely due to the fact that the mask (the native oxide at the silicon surface) has worn out at this point. The fact that the etch depth stays at a more or less constant level at etching times over 200 minutes, can be explained by the fact that both the top and the bottom of the channels are now (anisotropically) etched at the same speed. Assuming an oxide thickness that can vary from 0.5 to 2 nm [8], this would give a selectivity of Si <110> over SiO<sub>2</sub> of at least 250:1.

## Diluted OPD 4262

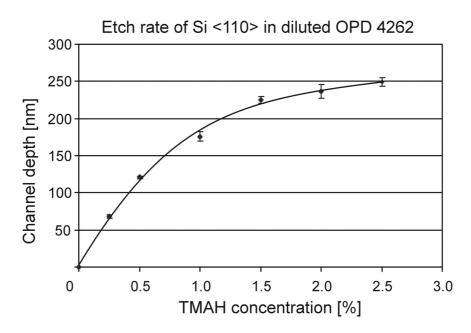

To try to bring down the etch rate even more, and thus to be able to create even smaller nanochannels, the effect of diluting the OPD 4262 solution was investigated. Seven different samples were etched in various concentrations of OPD 4262, ranging from pure OPD 4262 (2.5% TMAH) to pure DI water (which should not etch noticeably). The etched pattern consisted of 4 µm lines and spacings, like before. After 60 minutes of etching time, the channel depth on each of the samples was measured at three spots on the wafer. A graph of the etch depth versus TMAH concentration can be found in Figure 2-5.

Figure 2-5: Depth of trenches etched in silicon <110> using diluted OPD 4262 developer, after 60 minutes.

From this graph we can conclude that a 10% OPD 4262 solution in DI water is useable when very small channel heights are desired (e.g. below 50 nm). Inspection with optical microscopy showed a smooth surface after etching.

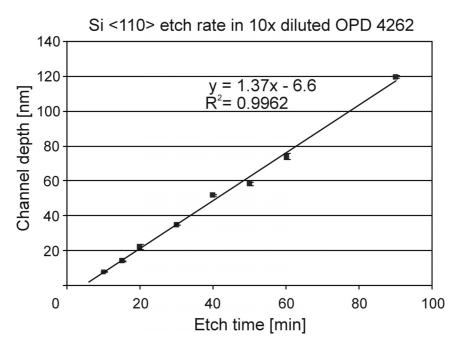

To confirm the applicability of the 10 times diluted OPD 4262 solution for creating sub-50 nm nanochannels, a time versus etch depth measurement was also done for this particular solution. The resulting etch rate calibration can be seen in Figure 2-6.

Figure 2-6: Etch rate of silicon <110> in 10x diluted OPD 4262 developer (0.25% TMAH).

From this graph, the etch rate of Si <110> in 10x diluted OPD 4262 can be calculated: this is 1.4 nm/min. There is a noticeable x-axis offset of approximately 5 minutes at the onset of the etching process. There are two possible explanations for the occurrence of this effect. One is that there could be a very thin layer of native oxide which is formed in the short period of time in which the wafer is exposed to air (when blow-drying the wafers after the IPA cleaning step) before the OPD 4262 etching step. In this case, also the 100% OPD 4262 solution should have an offset (of 1-2 minutes), which is very well possible, inspecting the data in Figure 2-4. Another explanation could be that the surface of the wafer is hydrogen terminated after the 1% HF etching of the native oxide. In this case, the surface has to become OH-terminated in water before the actual silicon etching can take place [9]. In any case, this offset can lead to greater non-uniformity and roughness, especially if the

etching times are small. When channels with a (well defined and predictable) depth of less than 20 nm are desired, other fabrication techniques might be preferred (e.g. by growing and selectively etching of a thin SiO<sub>2</sub> layer: see paragraph 2.2).

# 2.1.5 Direct bonding of etched wafers to silicon and Borofloat glass

Si < 110 > to Si < 110 > direct bonding procedure

Before bonding, both the etched wafer and the cover wafer undergo a 1% HF dip, a standard cleaning (10 min in fuming (100%) HNO<sub>3</sub>, followed by 10 minutes in boiling (69%) HNO<sub>3</sub>) and an additional Piranha cleaning to clean the silicon surfaces and to grow a well-controlled layer of native oxide on the silicon wafer surface. Then, the etched wafer is bonded to the <110> silicon cover wafer (prebond). After prebonding, the bond is annealed for 2 hours at 1100°C. This direct bonding procedure resulted in an instantaneous, near-perfect bond under an infrared camera. The high temperature needed in silicon-to-silicon fusion bonding (which can be unwanted when using certain materials in a device) can be prevented by using different bonding schemes such as anodic bonding to Pyrex wafers, or direct bonding to Borofloat wafers.

# Si <110> to Borofloat glass direct bonding procedure

The etched silicon wafers are also direct-bondable with Borofloat glass wafers. Before bonding the silicon and Borofloat wafers go through a standard cleaning, and a Piranha cleaning step. After manual prebonding the bond is then strengthened by an anneal step of 4 hours at 400°C. This annealing temperature of the silicon-to-glass bond is sufficiently low to prevent plastic deformation of the glass (and thereby possibly closing of the nanochannels) and interference of the bonding process with previous micromachining steps.

The silicon-to-Borofloat bond formed an almost complete prebond by manually pressing the wafers together. After the anneal step only very few bonding defects could be observed.

# 2.1.6 Channel fabrication and bonding results

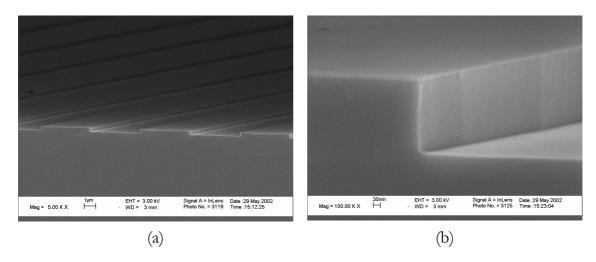

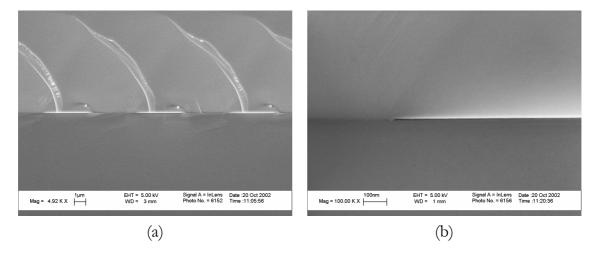

As an example of etched trenches, Figure 2-7 shows a channel with a step height of 335 nm. The near 90° sidewalls can be clearly seen, as well as the smooth walls and trench bottom.

# Etch depth uniformity

The uniformity of the etch depth over a complete wafer was also measured and was found to be good: measuring five points across a 4" wafer showed a variation of  $\pm$  1 nm at an etch depth of approximately 50 nm (the wafers were etched for a time of 13.5 minutes). This means that the uniformity is within  $\pm$  2%.

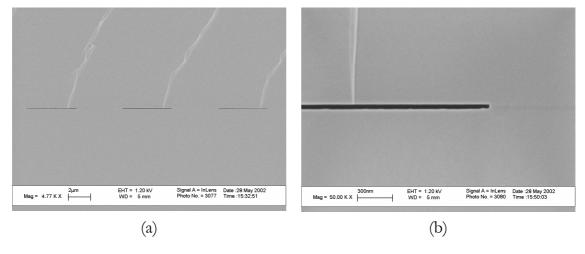

**Figure 2-7:** High resolution SEM pictures of trenches with a depth of approximately 335 nm, etched in <110> silicon. (a) Overview of multiple channels. (b) Close-up.

# Surface roughness

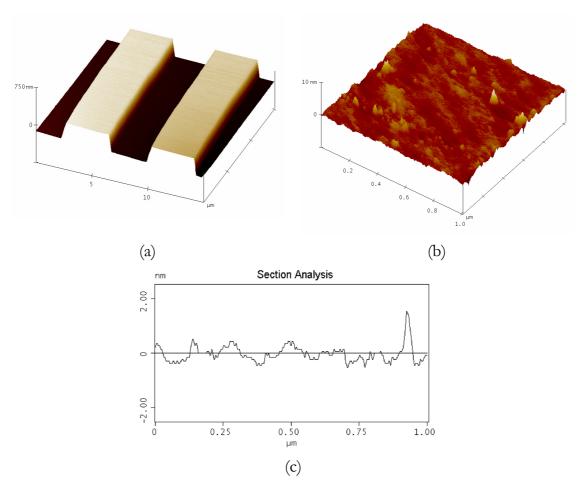

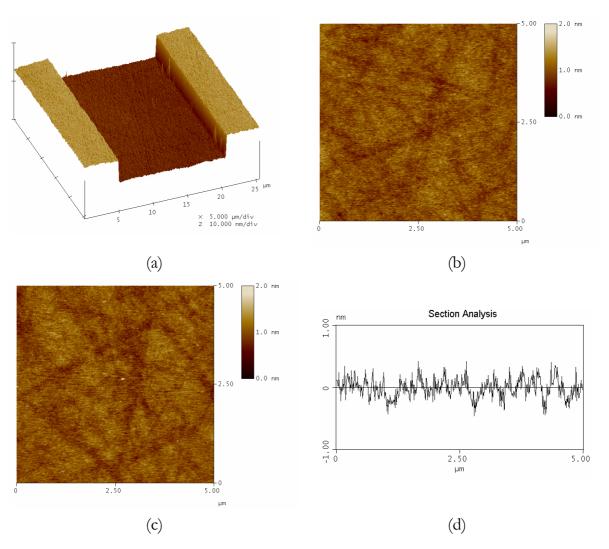

The surface roughness on the trench bottom was measured by contact mode AFM, and was found to be approximately 0.3 nm RMS, or 0.4 nm R<sub>a</sub> for the 335 nm deep trenches (see Figure 2-8).

# Bonding results

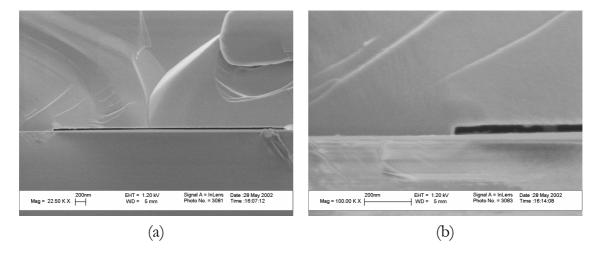

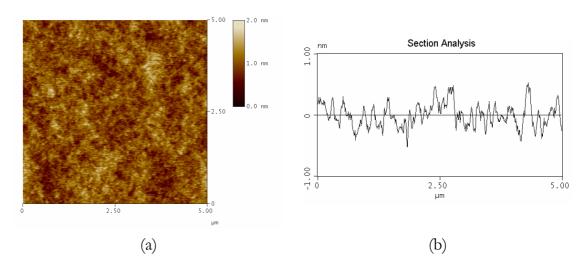

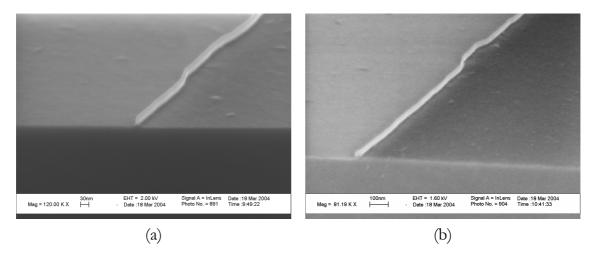

Pictures of the cross-section of the silicon-to-silicon bond can be seen in Figure 2-9. The curved ridges on the top wafer in Figure 2-9(a) are due to the breaking of the wafer, resulting from a non-perfect alignment of the two wafers during bonding. The straight etch profile can again be seen in Figure 2-9(b). As mentioned before, the silicon wafers with trenches were also bonded to Borofloat glass wafers. Cross-sections of the resulting structures can be found in Figure 2-10.

Figure 2-8: AFM pictures of trenches with a depth of 335 nm, etched in <110> silicon. (a) 3D view. (b) Roughness measurement on the bottom of a trench. (c) Section view of (b), showing the roughness more clearly.

Figure 2-9: SEM pictures of a wafer with 50 nm deep trenches, fusion bonded to a second <110> silicon wafer.

(a) Cross-section of 3 channels. (b) Close-up.

Figure 2-10: SEM pictures of a wafer with 50 nm deep trenches, fusion bonded to a Borofloat glass wafer. (a) Cross-section of one channel. (b) Close-up.

As can be seen in the SEM pictures, the channels are completely open and no significant bending of the wafers occurs, leaving the desired rectangular cross-sectioned channels.

### 2.1.7 Conclusions

A simple process to anisotropically etch channels with a controlled depth up to 500 nm has been developed. Olin OPD 4262, a standard resist developer consisting of 2.5% TMAH and surfactants, is suitable as an etchant for the anisotropic etching of nanochannels with a rectangular cross-section in a silicon <110> wafer. OPD 4262 etches Si <110> at a rate of 3.7 nm/min at room temperature. If necessary, it can be diluted ten times, to obtain an etchant with an etch rate of 1.4 nm/min.

Native oxide proved to be a suitable mask material to fabricate nanochannels with a depth up to approximately 500 nm (for deeper channels, a thin thermal SiO<sub>2</sub> layer could be grown to act as the mask material).

The uniformity of the etch depth across a wafer was observed to be within  $\pm$  2%. Moreover, surface roughness on etched surfaces could not be observed with SEM, and contact AFM measurements indicate a roughness value below 0.5 nm, which is very low.

38 Chapter 2

Furthermore, the etched wafers were successfully bonded to silicon <110> and Borofloat glass wafers to seal the channels.

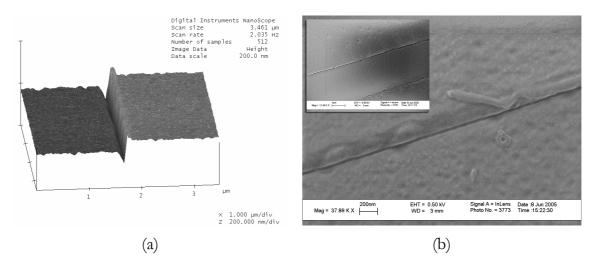

### 2.2 Fabrication of nanochannels using a dry oxide spacer layer

As an alternative and addition to the fabrication of nanochannels by using bulk silicon machining, as described in the previous section, nanochannels can also be produced by first growing an ultrathin (5-50 nm) layer of thermal oxide, and then patterning this layer in buffered hydrofluoric acid (BHF), or dilute 1% HF. If the oxide thickness and the etching of the layer are well-controlled, this enables the very accurate production of channels with a height below 50 nm, and even below 10 nm. This would eliminate for instance the start-up effect, as observed when etching with diluted OPD 4262, which has its largest influence in this etch depth range. Another aspect is that the measurement of the channel depth can be done using very accurate optical techniques (ellipsometry), whereas the mechanical surface profilometry (used to characterize the wet etched channels from the previous paragraphs) becomes less accurate at these very small dimensions. A disadvantage of this technology is that the isotropic underetching of the mask limits the line width which can be obtained (when compared to the OPD 4262 etching method).

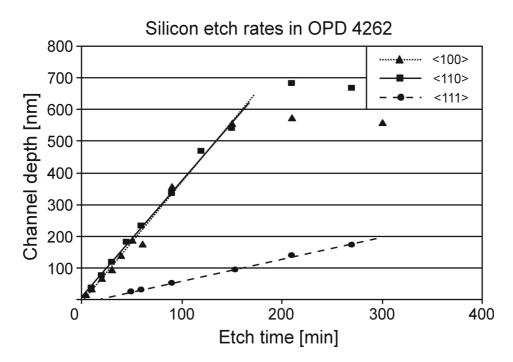

### 2.2.1 Basic fabrication process

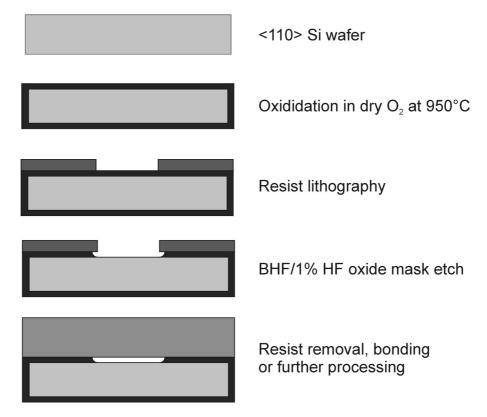

The basic fabrication process for creating sub-50 nm 1D fluidic nanochannels, using dry oxide as a spacer layer, is depicted in Figure 2-11.

The process is largely the same as the one used for the wet anisotropic etching of silicon (Figure 2-3). The main differences here are that the <110> silicon wafer is first oxidized at a temperature of 950°C, and no silicon etch step is included in this process (the channels are etched into the dry oxide spacer layer by means of wet etching in BHF or 1% HF: for this the resist layer undergoes a hardbake at a temperature of 120°C, for a period of 30 minutes).

Notice that the resulting cross-section of the channels will not be rectangular; this is because of the isotropic SiO<sub>2</sub> etching process, using (B)HF.

Figure 2-11: Basic process for the fabrication of nanochannels using a dry oxide spacer layer.

### 2.2.2 Dry oxidation of silicon

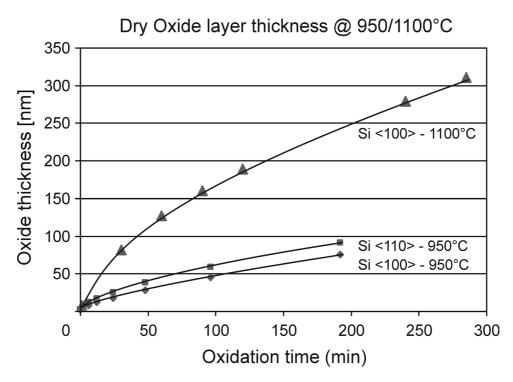

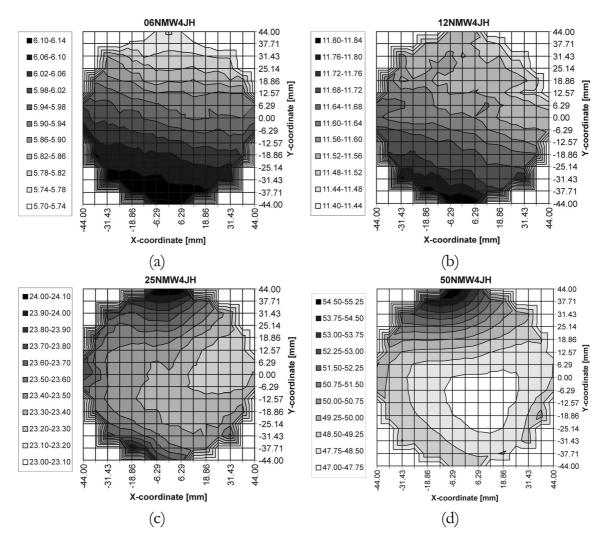

It is very important to have control over the thickness of the SiO<sub>2</sub> spacer layer, which will ultimately determine the height of the nanochannels. This layer is formed by oxidizing <110> wafers in dry oxygen at a temperature of 950°C. The reason why dry oxidation was chosen is that dry oxide layers generally show good thickness uniformity and very smooth surface finish. The chosen temperature of 950°C is lower than the usual 1100°C, to reduce the SiO<sub>2</sub> growth rate, and thus to be able to reproducibly grow layers with a thickness of ultimately less than 10 nm. For this purpose, silicon oxidation rates in dry oxygen at 950°C were measured: a graph of the oxide thickness versus time can be found in Figure 2-12 (for comparison, also the oxidation rate for Si <100> at 1100°C is shown).

**Figure 2-12:** Dry oxide thickness as a function of oxidation time at  $950^{\circ}$ C (the values for  $1100^{\circ}$ C are for comparison only, and were taken from the MESA<sup>+</sup> clean room database).

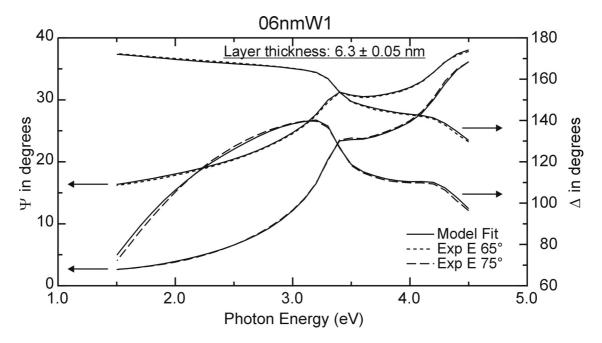

For our experiments silicon <110> wafers were dry oxidized at 950°C for different durations. Following oxidation, the oxide layer thickness was measured by ellipsometry. This was done on three separate ellipsometers: a Plasmos SD 2002 ellipsometer ( $\lambda = 632.8$  nm, or 1.96 eV), a multi-wavelength Woollam M-44 NIR ellipsometer (44 wavelengths ranging from 1.3 eV to 2.1 eV) and a Woollam variable angle spectroscopic ellipsometer (VASE, wavelength from 1.5 to 4.5 eV, used at angles of 65° and 75°). The results of the thickness measurements on wafers with target oxide thicknesses of 6, 12, 25 and 50 nm can be seen in Table 2-III.

| <110> Si<br>wafer ID | Oxidation time [min:s] | Target<br>[nm] | Plasmos<br>[nm] | Woollam<br>M44 [nm] | Woollam<br>VASE [nm] |

|----------------------|------------------------|----------------|-----------------|---------------------|----------------------|

| 06nm                 | 01:15                  | 6              | $6.2 \pm 0.5$   | $6.1 \pm 0.05$      | $6.3 \pm 0.05$       |

| 12nm                 | 05:30                  | 12             | $11.9 \pm 0.5$  | $11.9 \pm 0.04$     | $12.1 \pm 0.05$      |

| 25nm                 | 22:30                  | 25             | $23.9 \pm 0.5$  | $24.1 \pm 0.03$     | $24.3 \pm 0.05$      |

| 50nm                 | 75:00                  | 50             | 49 ± 1          | $49.0 \pm 0.03$     | 49.1 ± 0.05          |

Table 2-III: Oxidation times, target and measured dry oxide thicknesses on three different ellipsometer systems.

The Plasmos ellipsometer is very suitable for locally determining oxide thickness, as it has a programmable (x,y)-stage, as well as a very small spot size (approximately 1 mm in diameter). While the two other systems are supposed to have a greater accuracy (due to the use of multiple wavelengths and angles of incidence), the measured values correspond with those given by the Plasmos ellipsometer.

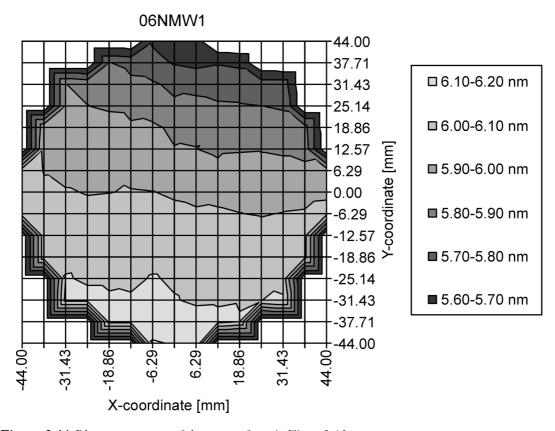

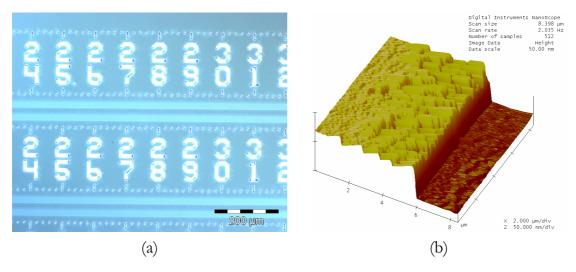

Figure 2-13 and Figure 2-14 show two measurements of the same wafer: the former was done on the Woollam VASE ellipsometer (measurement spot in the middle of the wafer), the latter is a raster scan, as produced by the Plasmos system.

Figure 2-13: Woollam variable angle spectroscopic ellipsometer data for an oxide layer on <110> silicon, with a measured thickness of 6.3 nm.

Figure 2-14: Plasmos raster scan of the same wafer as in Figure 2-13.

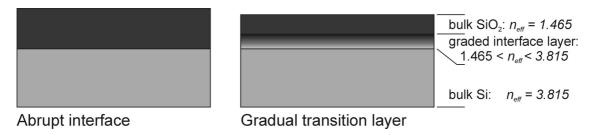

The ellipsometer systems which have been tested all give the same values for oxide thickness, within their experimental errors. However, there is the matter that extremely thin oxide layers have sometimes been observed to have refractive indices that largely deviate from the theoretical value at 632 nm (n = 1.465, which has been assumed in the current experiments). As an example, Hebert et al. [10] found an effective refractive index of 1.9 for ultrathin (4-6 nm) silicon dioxide layers using Fowler-Nordheim tunneling current oscillations and ellipsometry. The idea behind most of the deviations from the bulk value of the refractive index is that a non-instantaneous transition between Si and SiO2 is assumed. Instead a gradual transition layer with a higher refractive index than oxide, but lower than silicon, is modeled: see Figure 2-15. This results in a lower oxide thickness measurement result. Kao and Doremus, for instance, measured the thicknesses of thin oxide films by Transmission Electron Microscopy (TEM), ellipsometry, and profilometry. The results from these three methods corresponded for thicknesses over 30 nm. When the film thickness was smaller than 30 nm, the thickness as measured by ellipsometry was larger than the values obtained by TEM. The results

could be described by a two-film model, with an interfacial layer of 1.2 nm having a refractive index of 2.5, and a bulk  $SiO_2$  film with the bulk refractive index [11]. Cho et al. [12] presented similar results for  $SiO_2$  layers between 12 and 150 nm. On the other hand, Chao et al. studied sub-10 nm  $SiO_2$  films by variable angle ellipsometry [13], and concluded that an abrupt interface is the most appropriate model, combined with an increase in refractive index, albeit an almost negligible one (they found n = 1.47 for a 10 nm thick film, grown at 950°C).

**Figure 2-15:** Model for a non-uniform  $SiO_2$  layer: in the picture on the right the physical thickness of the layer is less than would be measured based on the (ideal) model on the left.

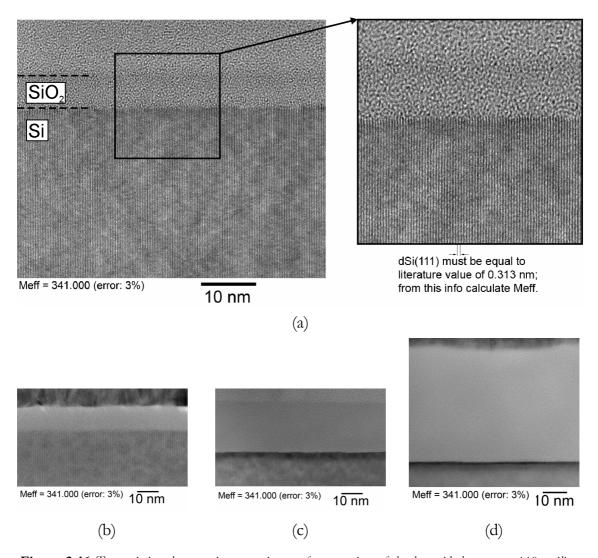

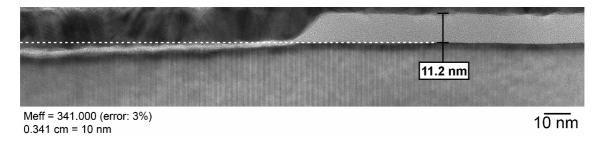

To check whether the physical oxide thickness is really consistent with the ellipsometrically found values, TEM measurements were performed on the four wafers. Pictures of the TEM cross-sections of each of the SiO<sub>2</sub> layers can be seen in Figure 2-16. Each image was calibrated by measuring the distance between the Si <111> planes in the picture: this has to be equal to the literature value of 0.313 nm. After measuring the SiO<sub>2</sub> thickness from the pictures, a comparison between TEM and ellipsometry was made: see Table 2-IV.

| Ellipsometer thickness [nm] | TEM thickness [nm] |

|-----------------------------|--------------------|

| $6.1 \pm 0.5$               | 6                  |

| $11.8 \pm 0.5$              | 11.1               |

| $23.8 \pm 0.5$              | 23.6               |

| 48 ± 1                      | 47                 |

**Table 2-IV:** Comparison between ellipsometer and TEM measurements, indicating reliable ellipsometer values.

Figure 2-16: Transmission electron microscope pictures of cross-sections of the dry oxide layers on <110> silicon.

(a) 6 nm thickness. (b) 12 nm thickness. (c) 25 nm thickness. (d) 50 nm thickness.

The conclusion of these measurements is that the ellipsometer measurements correspond with the TEM measurements. The significant deviations in refractive index as found by some other groups, do not seem to occur for these layers.

In summary, well defined dry oxide layers with a thickness of 5-50 nm can be produced by oxidation of Si <110> wafers at a temperature of 950°C. Characterization of these layers by ellipsometry was shown to be an accurate and reproducible method.

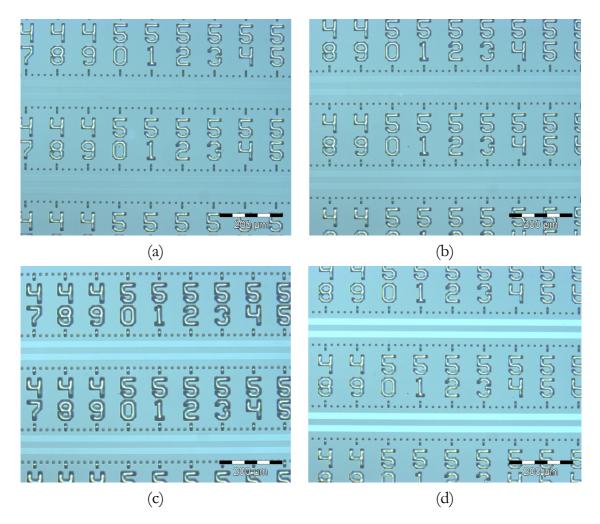

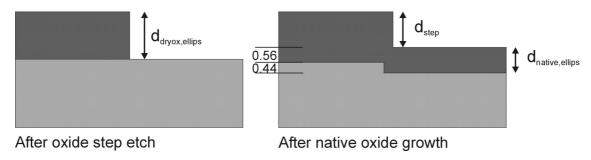

### 2.2.3 (B)HF etching of channels

Initially, after resist spinning and exposure using a mask containing 4 µm wide lines, followed by a hard bake of the resist, channels were etched in the oxide (wafers with layers of 6, 12, 25 and 50 nm of dry SiO<sub>2</sub>) using BHF (NH<sub>4</sub>F/HF (1:7)) as the etchant. The etch time was 90 s for all wafers (the etch rate of thermal oxide in BHF is approximately 70 nm/min). All wafers showed a hydrophobic backside after etching, indicating that the oxide layer was completely etched. After etching the photoresist was stripped in fuming nitric acid. Following this, the wafers went through a standard cleaning in nitric acid (10 min in fuming HNO<sub>3</sub>, 10 minutes in boiling HNO<sub>3</sub>). This standard cleaning forms new layer (1-2 nm) of native oxide on the bottom of the channel. Due to this native oxide growth, the channel depth is decreased with an amount of 0.56 times the native oxide thickness. This is because the native oxide "grows" out of the channel bottom [8]. The expected resulting channel depth can then be predicted by:

$$d_{channel} = d_{drv \text{ oxide}} - 0.56 \cdot d_{native \text{ oxide}}$$

(2.1)

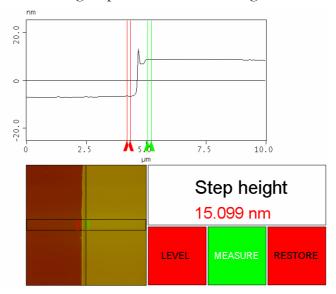

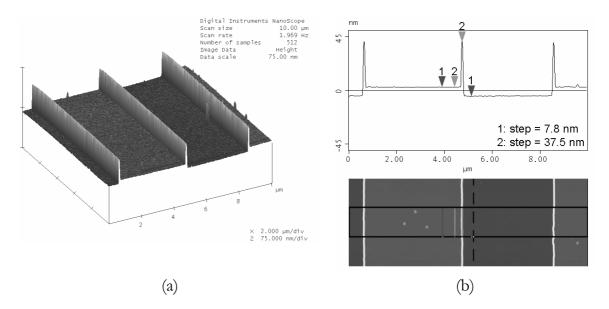

After etching in BHF and subsequent wafer cleaning, channel depths were measured using both AFM and ellipsometry (according to equation (2.1)). An AFM picture of one of the resulting steps can be found in Figure 2-17.

Figure 2-17: AFM measurement of a step etched in a wafer with an oxide layer with a thickness of approximately 12 nm. The resulting channel depth is larger than expected based on equation (2.1).

A summary of all measured values can be found in Table 2-V: note that the oxide thickness values differ from those in Table 2-III, because the measurements steps in Table 2-V were not done at the centre position of the wafer, but at another location (the oxide thickness was also measured for this position).

| Wafer ID | Ellipsometer                   |                                   |                              | AFM              | Comparison         |

|----------|--------------------------------|-----------------------------------|------------------------------|------------------|--------------------|

|          | d <sub>dry oxide</sub><br>[nm] | d <sub>native oxide</sub><br>[nm] | d <sub>channel</sub><br>[nm] | Step height [nm] | Difference<br>[nm] |

| 06nm     | $6.1 \pm 0.5$                  | $2.2 \pm 0.5$                     | $4.8 \pm 0.8$                | $9.0 \pm 0.9$    | 4.2                |

| 12nm     | $11.9 \pm 0.5$                 | $2.2 \pm 0.5$                     | $10.7 \pm 0.8$               | 15.1 ± 1.5       | 4.4                |

| 25nm     | $23.9 \pm 0.5$                 | $2.2 \pm 0.5$                     | $22.7 \pm 0.8$               | 27.2 ± 2.7       | 4.5                |

| 50nm     | 48 ± 1                         | $2.2 \pm 0.5$                     | 47 ± 1.3                     | 52.2 ± 5.2       | 5.6                |

**Table 2-V:** Calculated step heights (based on ellipsometry measurements) compared to measured step heights (measured by AFM) after etching for 90 seconds in BHF.

From the last two columns, it is obvious that there is a large discrepancy between the ellipsometer-based values and the AFM values. The measurement error in the expected channel depth based on the ellipsometer measurements is approximately 1 nm. The AFM was calibrated using a sample containing 0.39 nm high steps of STO (Strontium Titanate:  $SrTiO_3$ ), the error is estimated to be  $\pm$  10% of the measured value.

The explanation for the differences in expected and measured values could be that the BHF does not stop exactly on the interface of silicon and silicon dioxide, but that it etches further, into the "bulk" silicon. Therefore the etching behavior of BHF in comparison to various concentrations of HF was investigated.

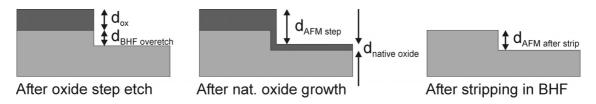

### 2.2.4 BHF overetch determination

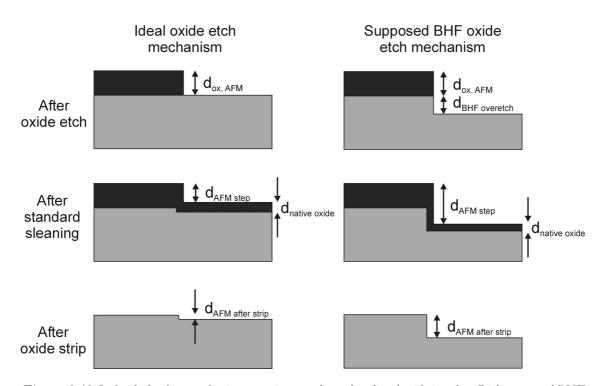

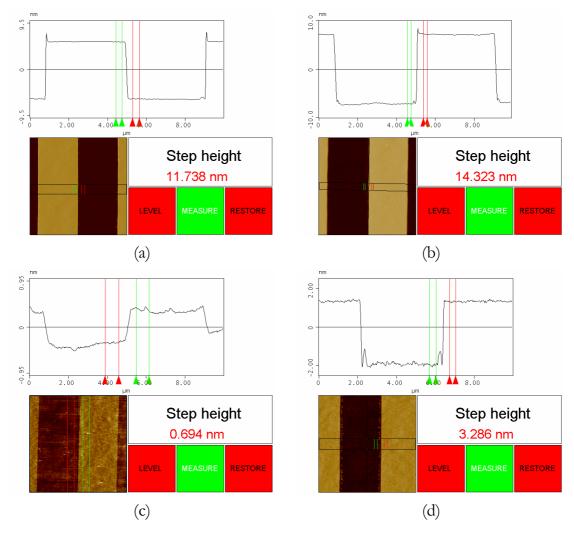

For an investigation into the etching behavior of (B)HF on thin oxide layers, an experiment was designed to compare the influence of etching with various solutions (BHF, 1% HF, 2% HF, 5% HF). The general idea behind the experiment can be seen in Figure 2-18.

The process consists of the following steps:

- 1. Dry oxidizing <110> Si wafers.

- 2. Photolithography (4 µm lines and spaces mask).

- 3. (B)HF etching of the dry oxide layer.

- 4. Standard cleaning of wafers.

- 5. AFM measurement of step height ( $d_{AFM step}$ ).

- 6. Strip the sample in the same time (and in the same etching solution) as in step 3.

- 7. AFM step height measurement after stripping ( $d_{AFM after strip}$ ).

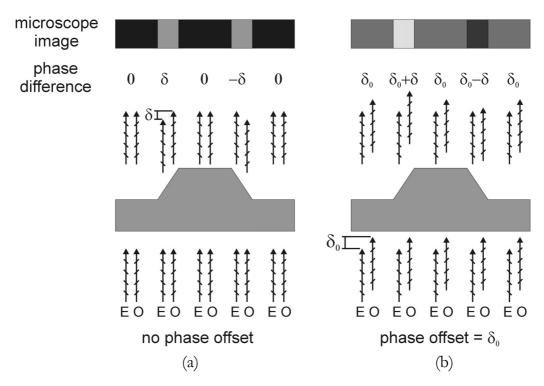

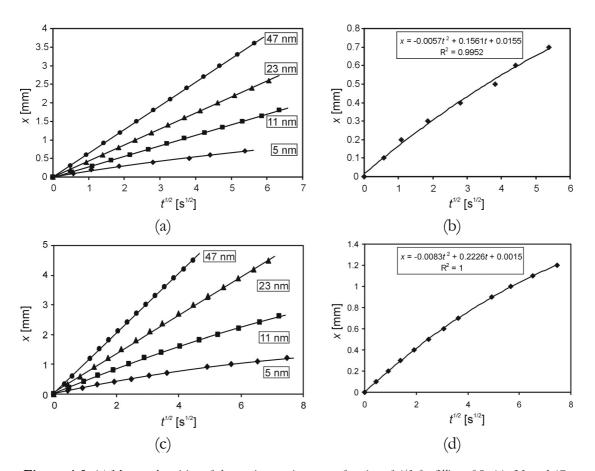

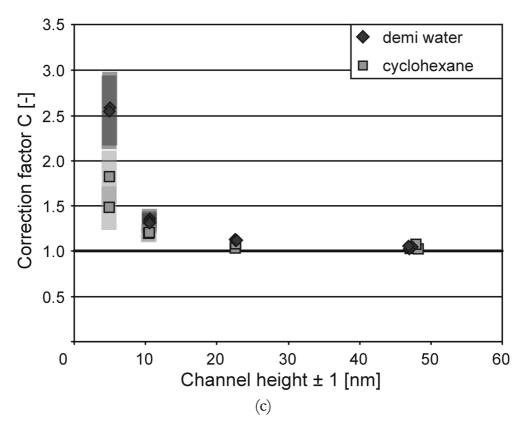

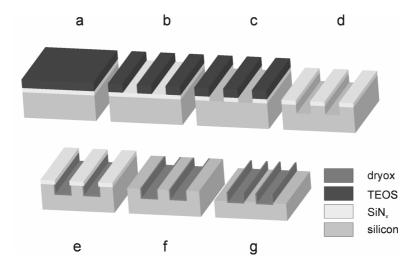

**Figure 2-18:** Left: ideal etching mechanism, stopping exactly on the silicon/oxide interface. Right: proposed BHF oxide etching effect: after hitting the interface, the etching continues into the silicon substrate, creating a deeper trench.